# **R&D Status and Key Technical and Implementation Challenges** for EUV HVM

Sam Sivakumar

Intel Corporation

### Agenda

Requirements by Process Node

# EUV Technology Status and Gaps

- Photoresists

- -Tools

- -Reticles

# Summary

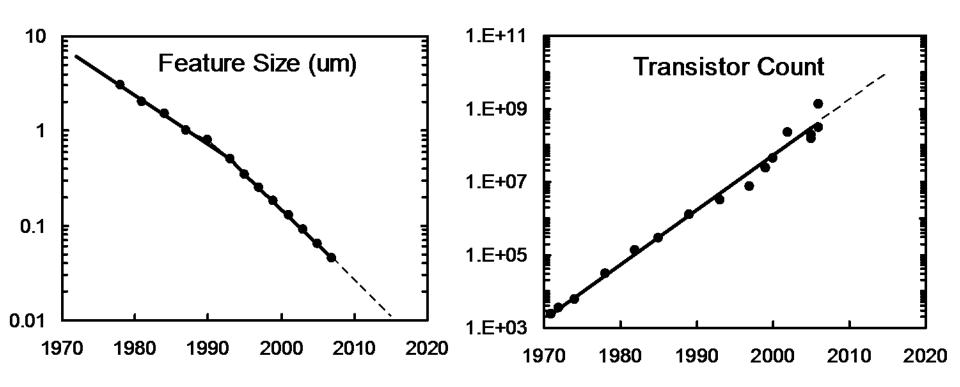

## **Moore's Law at Intel**

### The trend is expected to continue

3

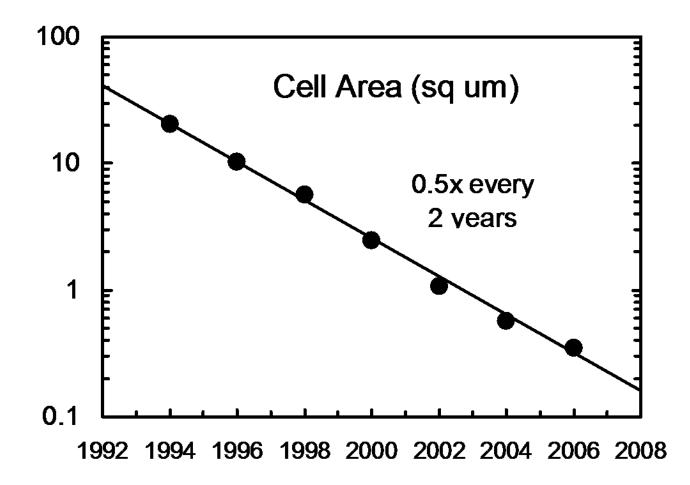

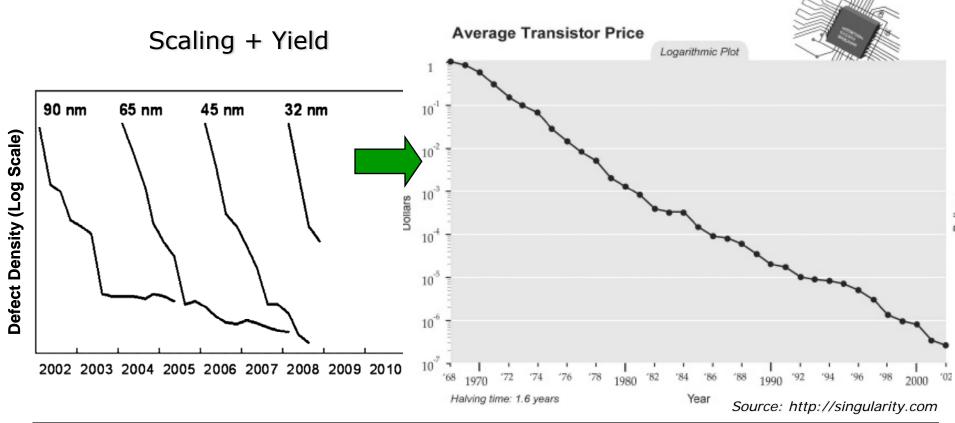

## **Transistor Density Trend**

# **On-Time 2 Year Cycle**

Sivakumar

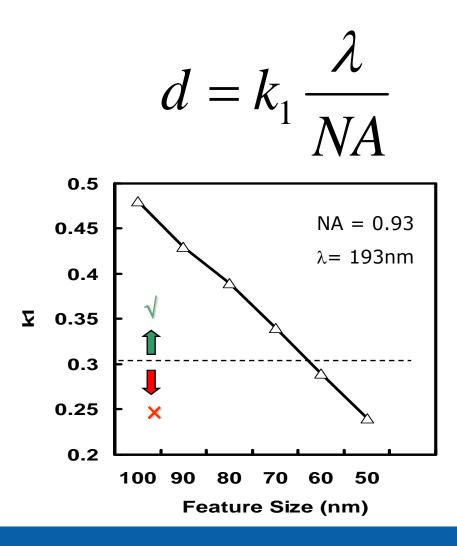

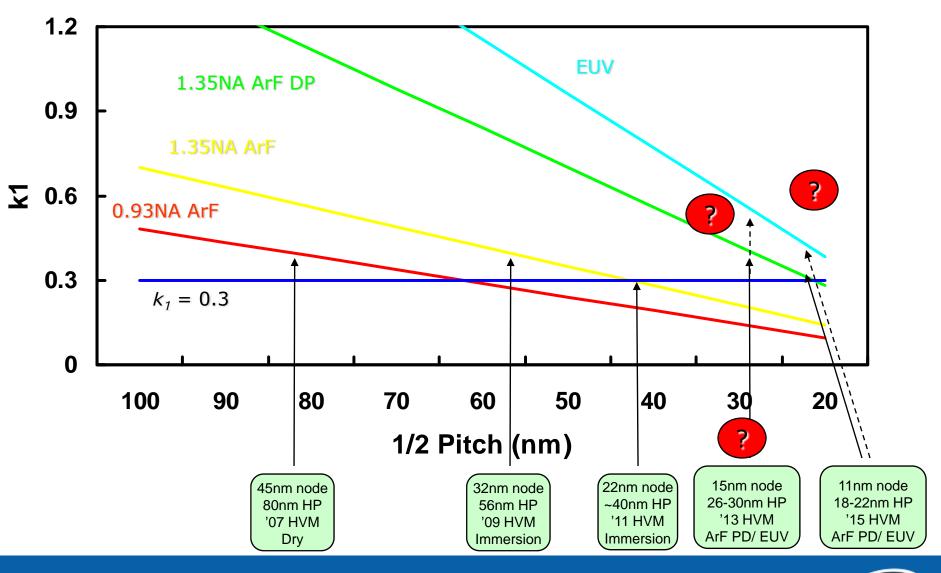

## **Paths to Feature Size Scaling**

Increase NA

Enable reduced pitches through process options (like double patterning)

Reduce Wavelength

k<sub>1</sub> < 0.3 tends to have manufacturability issues

Sivakumar

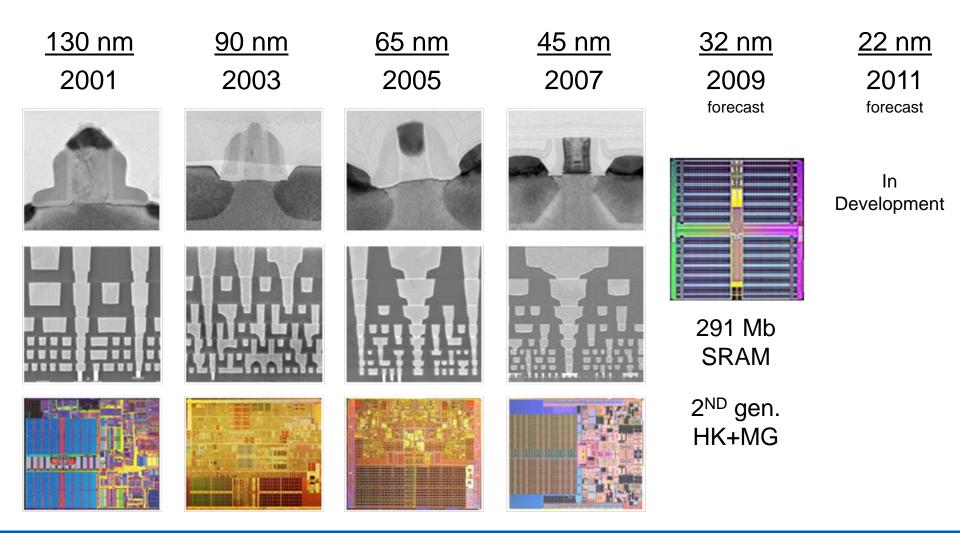

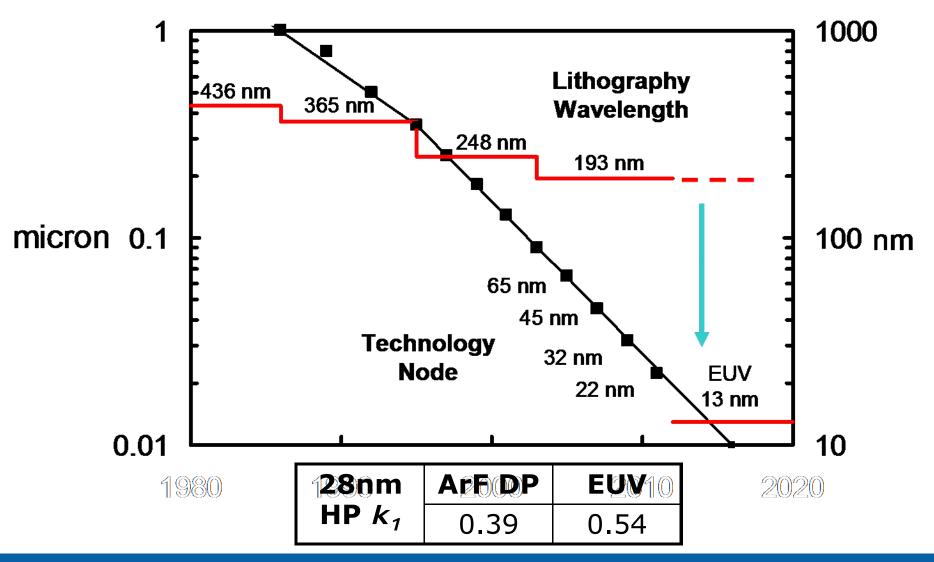

# **Lithography Transitions**

If current lithography is capable of delivering a manufacturable process, use it

If not:

- If new lithography technology is ready, manufacturable and cost-effective, use it (increase NA, reduce  $\lambda$ )

-If not:

- need to make alternative decisions to enable scaling without litho improvements (operate more effectively at lower  $k_1$ )

Managing litho transitions is key! Requires significant planning

7

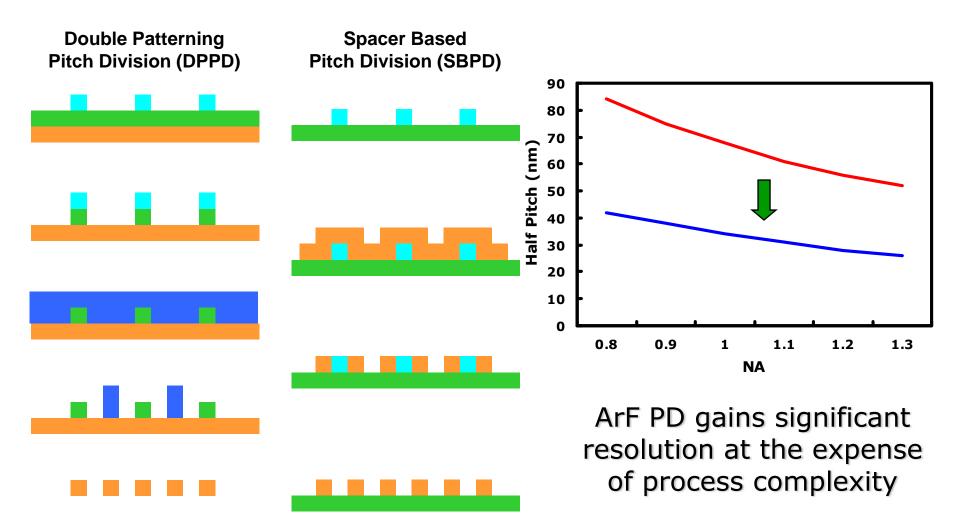

### **ArF Pitch Division vs. EUV**

Inte

# Patterning Choices for 15nm and 11nm

### **ArF Pitch Division**

### <u>EUV</u>

Advantages:

- Known technology

- Well-established infrastructure

- Mature photoresist and tooling

Disadvantages:

- Complex process flow

- Very expensive

- Complicated DRs

Advantages:

- Single exposure

- Simpler DRs

### Disadvantages:

- Unknown technology

- Infrastructure needs to be developed

- Immature photoresist, tooling

9

## **ArF Pitch Division**

## $\lambda$ Scaling – The Case for EUV

## **EUV HVM – Key Requirements**

Stable hardware

- Scanner platform

- Optics

- Overlay/stage

- System (vacuum)

- Source

- Reliability and uptime

- Power

- Photoresist that meets requirements

- Resolution, sensitivity, LWR

- Etch interactions

Reticles

- Defectivity

- Infrastructure (cleans, inspections, handling)

### Success of EUV in HVM will depend on progress on all these fronts

### **Exposure Tooling**

Sivakumar 13

## **EUV Exposure Tooling**

### External

### - Nikon EUV1 alpha tool

- 0.25NA full field scanner

- Currently installed at Nikon and SELETE

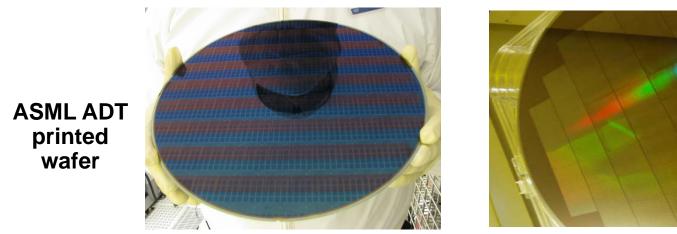

### - ASML Alpha Demo Tool (ADT)

- 0.25NA full field scanner

- Currently installed at IMEC and SEMATECH

### **Intel Internal**

- MET small-field exposure tool

- Target application is resist development

## **EUV HVM Exposure Tooling Development**

Nikon EUV1 printed wafer

### **EUV Source Suppliers are competing towards HVM tool development**

Cymer beta source

Philips beta source

Sivakumar 15

# Nikon EUV1 Tool

| AL TON                                       |

|----------------------------------------------|

|                                              |

| TRACE LANT                                   |

|                                              |

|                                              |

|                                              |

|                                              |

| CARL AND |

| Field Size           | 26 x 33 mm <sup>2</sup> |

|----------------------|-------------------------|

| NA and Magnification | 0.25, x1/4              |

| Illumination Sigma   | Adjustable              |

| Overlay              | 10 nm                   |

Sivakumar **16**

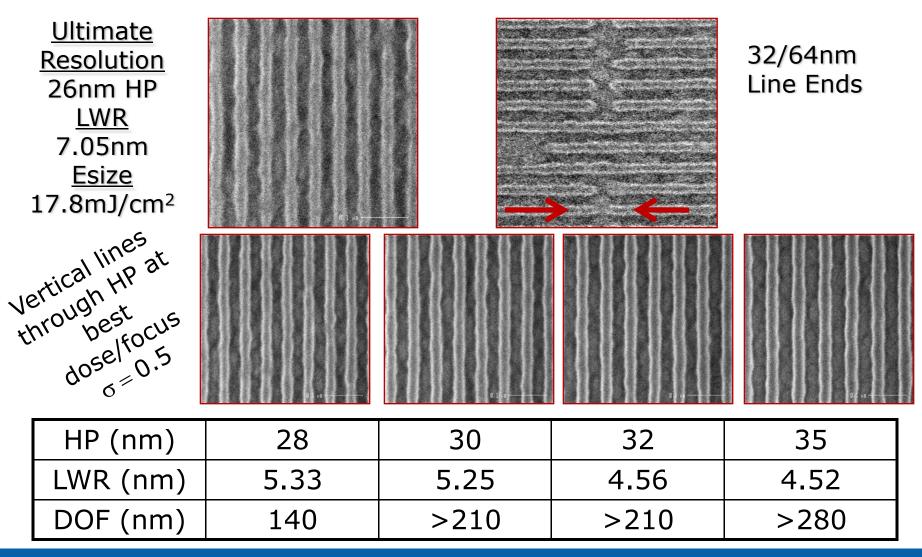

# Nikon EUV Tool Data – Lines (Static)

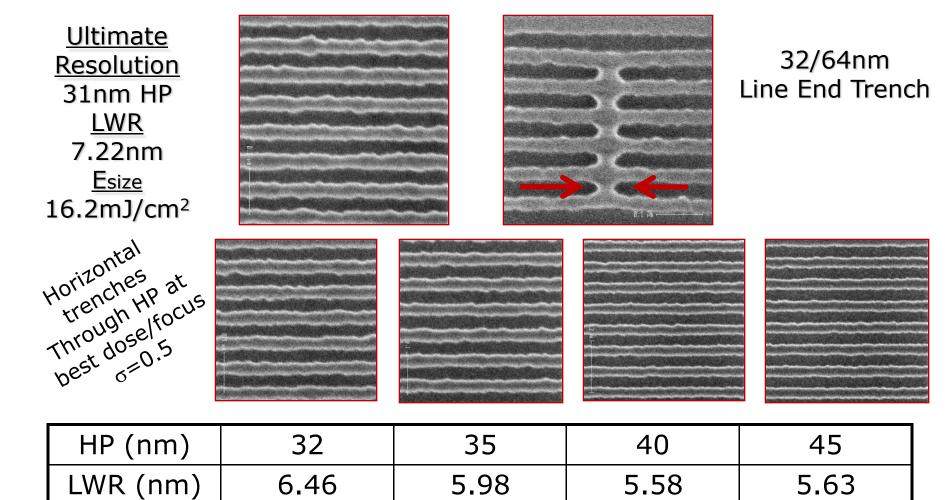

# Nikon EUV Tool Data – Trenches (Static)

DOF (nm)

>140

>160

>180

>100

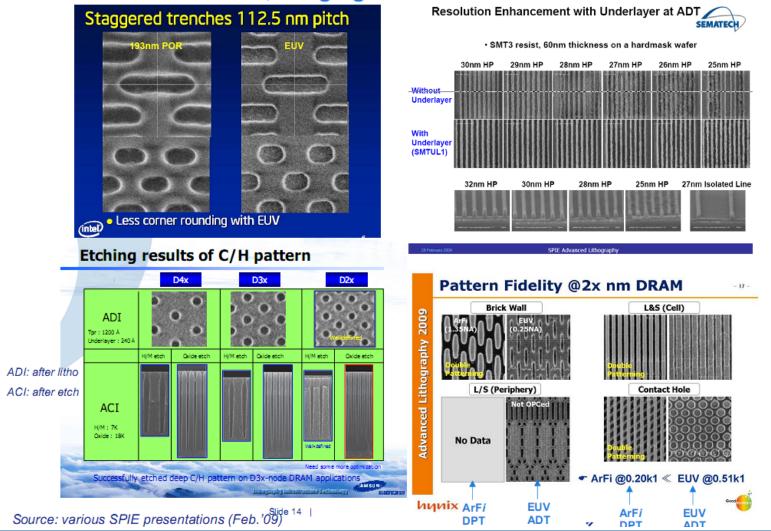

## **ADT Patterning Results**

### 25 nm HP resolved; imaging results from ADT

Sivakumar **20**

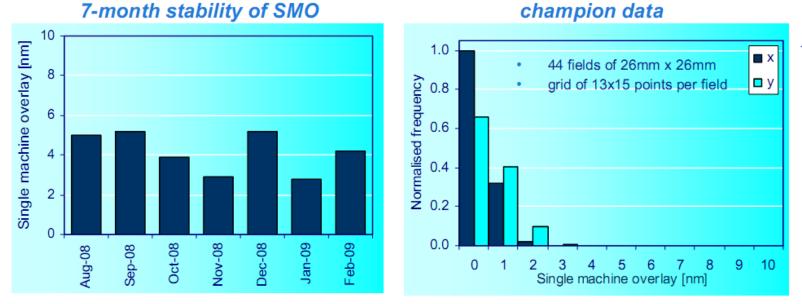

## **ADT Overlay Stability Data**

champion data single machine overlay (SMO) is 2.9 nm

<u>system characteristics</u>: 120 W/2π source ~4 wph @ 5 mJ/cm<sup>2</sup> dose

#### Sivakumar **21**

2009 International Workshop on EUV Lithography

Slide 10

### **Cymer LPP EUV Source**

Photo Courtesy of Nigel Farrar, Cymer, Inc.

Sivakumar **22**

## **Cymer EUV Source**

### FIRST CYMER LPP EUV SOURCE SYSTEM HAS SHIPPED

- Exposure Power >15-20W\*

- Exposure Power = Average Power

- 400ms burst length

- Equal to one die scan time

- 40% duty cycle

- Duty cycle limited by Far Field metrology (not the source)

- Dose control implemented

- 30µm droplet diameter

- 5 sr collector installed with higher reflectivity

- Debris mitigation validation completed

Source vessel shipment

| * Power in configu      | ration with a 5 sr collector, measure | <b>d at plasma assuming 50% average reflectivity and 90% transmission</b> |   |

|-------------------------|---------------------------------------|---------------------------------------------------------------------------|---|

| • • • • • • • • • • • • | • • • • • • • • • • • • • • •         | ····· CYMER                                                               | 1 |

| July 13, 2009           | 2009 LITHOGRAPHY WORKSHOP             | © 2009 Cymer, Inc.                                                        |   |

# **Philips DPP EUV Source**

### PHILIPS

### Alpha DPP sources in the field

24 DPP sources in use for wafer exposures and EUV R&D

- Many years of runtime: more than 60 billion DPP pulses used for exposures and source testing

- With 120Win2PI source, up to 4-5W IF power continuously scanning > 4 wafers per hour (5 mJ/cm2 resist)

- Reticle Collector Wafer Source

**XTREME**

Continuous Improvement Process ongoing to support customers (e.g. 170Win2PI)

Lithography Workshop, Idaho, June 29th, 2009

### **Photoresists**

Sivakumar **25**

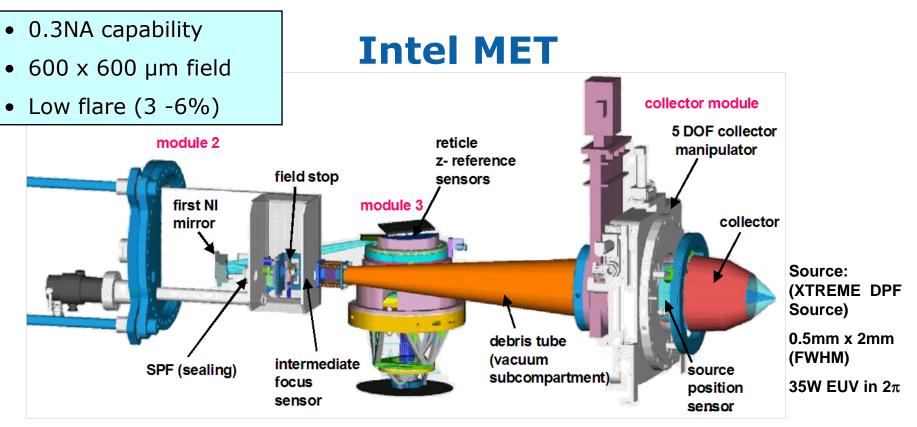

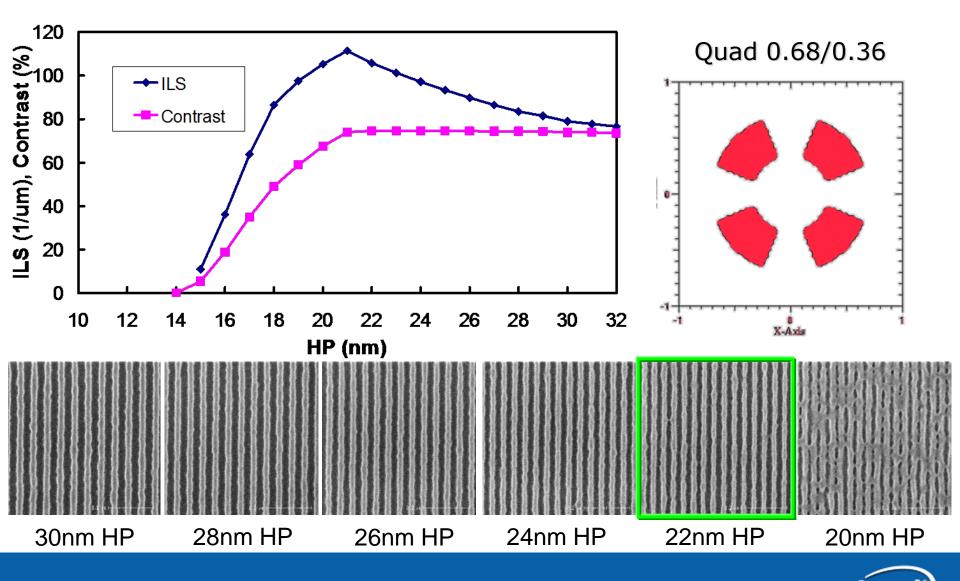

- New EUV collector installed

- $\bullet$  New outer shell extended  $\sigma$  outer from 0.55 to 0.65, 22nm HP resolution with quadrupole illumination

- First step in preparation for 0.5 NA MET projection optics (2010) that will enable ~10nm HP resolution

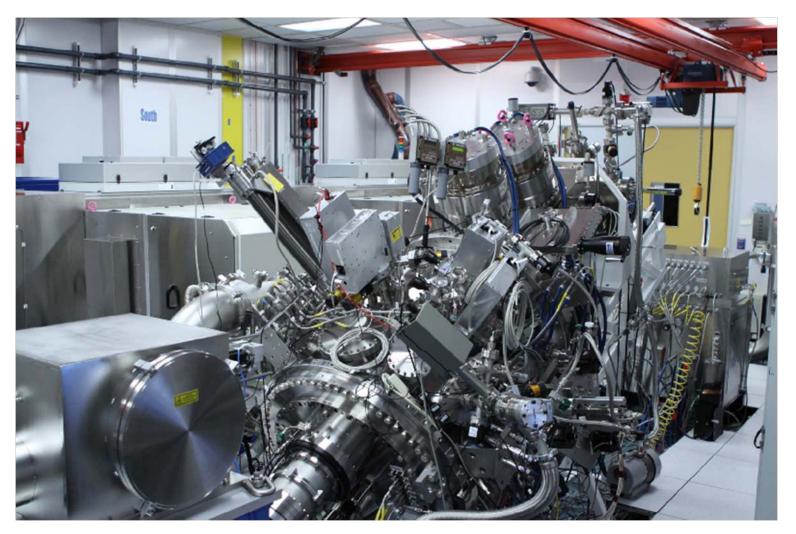

# **Intel MET Status**

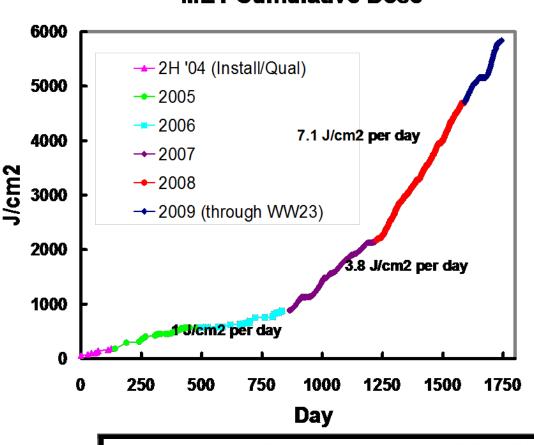

### MET Cumulative Dose

Uptime average: 67% in '07, 85% in '08, 63% through WW22 in '09

Continuous improvement in output efficiency – 13J/cm<sup>2</sup>/day currently

On track to deliver more dose in 2009 than in 2008

Improved resolution and expanded process window

Long term upgrade path defined down to  ${\sim}10\text{nm}$  HP

> 250 Resists Screened in '08. Goal <u>></u> 500 in '09

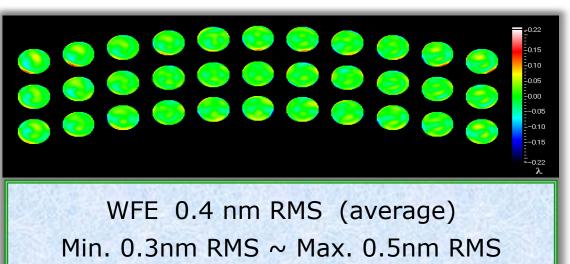

## **New MET Quad Source Enables 22nm HP**

2009 International Workshop on EUV Lithography

28

Sivakumar

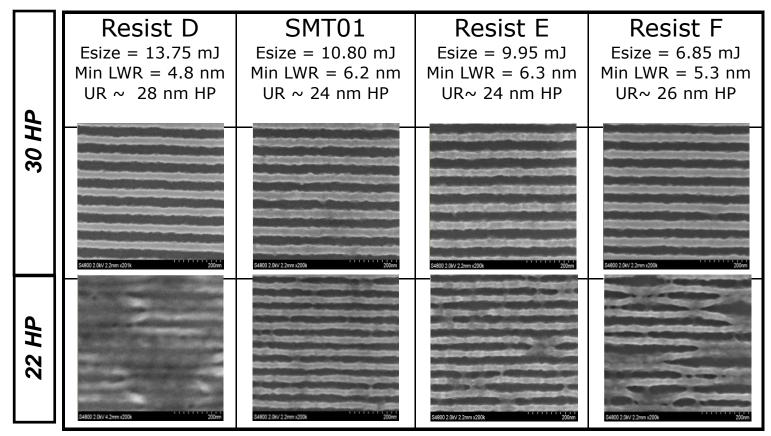

### Berkeley ALS-MET (Rotated Dipole) :: Champion RLS Summary for 30 + 22 hp

Champion CAR platforms Nominally Meeting 22nm HP R/S Targets but Failing for LWR/PC

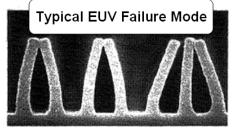

# **Pattern Collapse Margin Improvement**

Bending Failure

Capillary force exceeds the critical modulus of resist material.

### Pattern Collapse Mitigation is primary focus for 2009

Multiple approaches may be needed to address problem

- Modify Aspect Ratio

- Surface (Energy)Optimization: Hydrophobicity, Multilayer stacks

- Increased resist modulus, Negative Tone & Semi-organic Resists

- Decreased Surface Tension: Rinse agents, Organic Developers, Develop/Rinse/Spin Dry Process Optimization

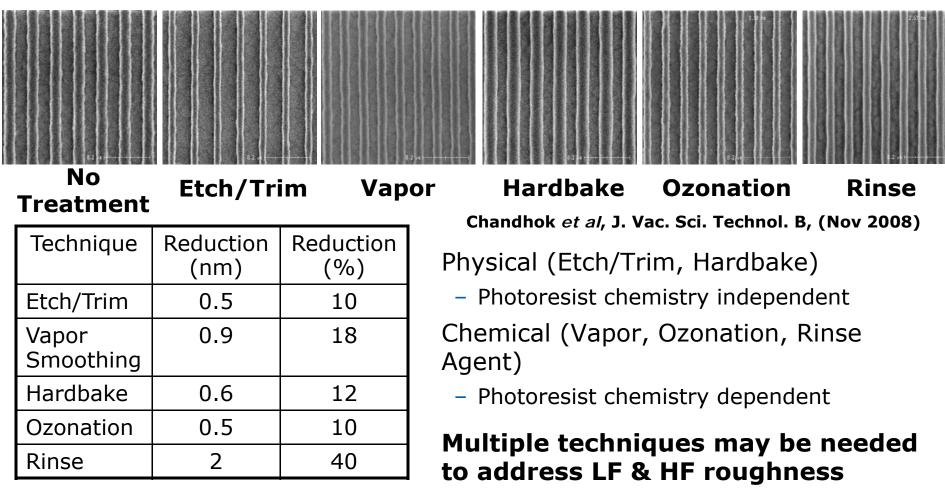

## **LWR Reduction Techniques**

### Largest LWR Improvement Seen with Rinse Agent

# **Resist and Tooling Gaps**

### Photoresists (32/22nm HP)

|                      | Photospeed (mJ/cm <sup>2</sup> ) | 3σ LWR (nm) |

|----------------------|----------------------------------|-------------|

| Current              | 10/20                            | 3.8/6.4     |

| Target               | 10                               | 1.9/1.28    |

| Improvement Required | None/2X                          | 2X/5X       |

### **Source Power**

|                         | Power (W) |

|-------------------------|-----------|

| Current                 | ~20       |

| Target                  | 200       |

| Improvement<br>Required | 10X       |

### **Scanner Runrate**

|                         | Runrate (wph) |

|-------------------------|---------------|

| Current                 | 5             |

| Target                  | 100           |

| Improvement<br>Required | 20X           |

### Summary:

Good progress made to date

Need continued work to bridge (or significantly reduce) gaps for both performance and COO

Sivakumar **33**

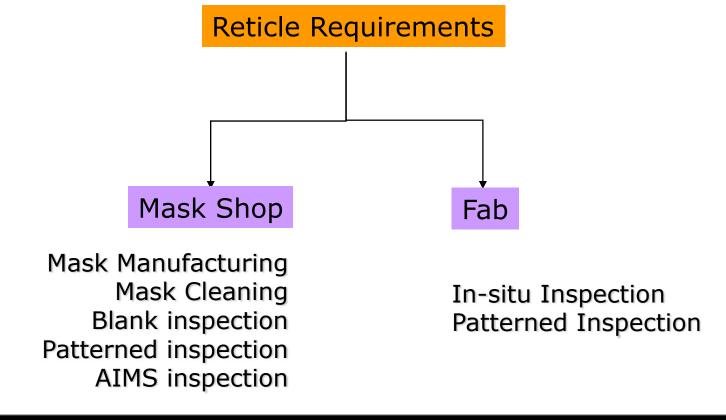

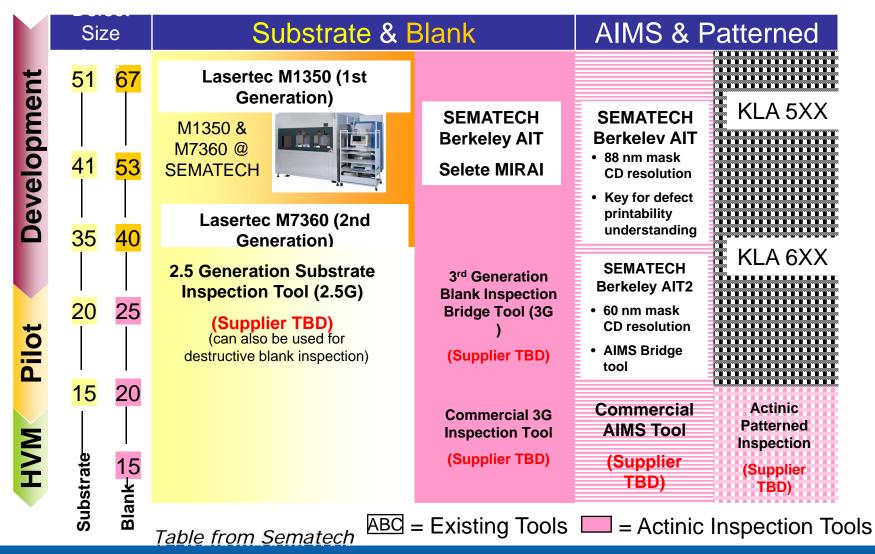

## **HVM Reticle Infrastructure Requirements**

### Need inspection capability in both the mask shop and the fab to ensure manufacturable operations

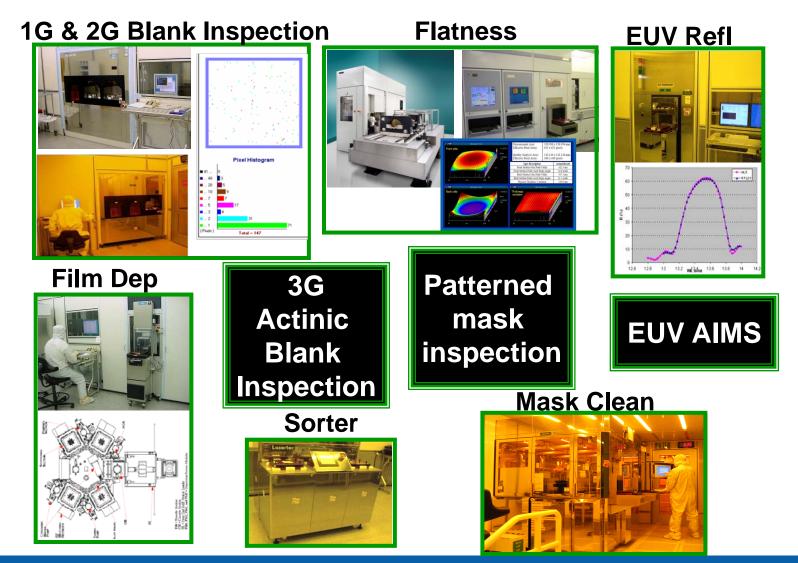

## **Intel's Mask Tool Pilot Line**

Sivakumar **35**

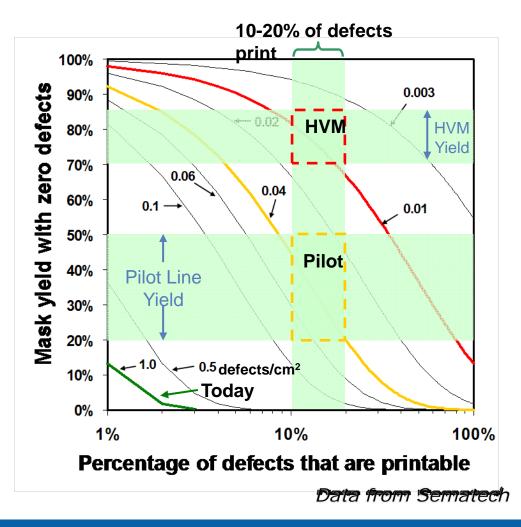

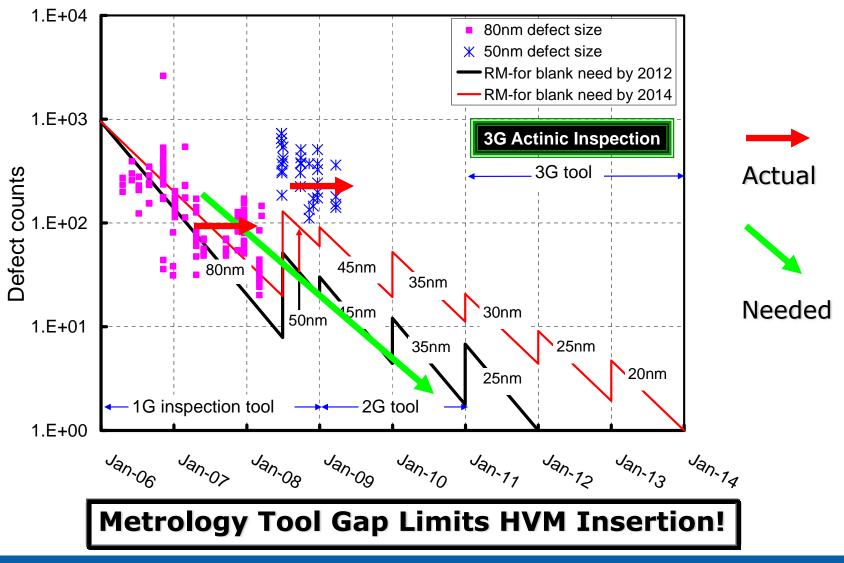

### Mask Blank Yield Gap for Pilot Line and HVM Introduction

### **Determine Defect Density Target**

- 0.003 defects/cm<sup>2</sup> @ 18 nm is the historical "defect free" target

- However, recent data suggests only 10-20% of defects print

- The ultimate HVM defect density target might be 0.01 defects/cm @ 18 nm

### Today: 1 defect/cm<sup>2</sup>@18nm

## Gap to Pilot: > 25x Gap to HVM: >100x

## **Mask Blank Defect Trends**

## **New Blank Defect Inspection Capability**

| Blank inspection tool    | G1 (M1350) | G2 (M7360) |       |

|--------------------------|------------|------------|-------|

| Laser source $\lambda$   | 488 nm     | 266 nm     |       |

| > 98% capture rate       | 2004-Q2′08 | Q3′08      | Q1′09 |

| Def. on quartz substrate | 70 nm      | 45 nm      | 35 nm |

| Def. on ML blank         | 80 nm      | 50 nm      | 40 nm |

2<sup>nd</sup>-gen mask blank inspection tool successfully installed in June

Inspectability will be further extended with spatial filter upgrade in Q4

Moving toward ultimate 25nm inspection requirement for 2010-11

## **AIMS and Patterned Defect Inspections**

### AIMS:

- Industry requirement:

- 22nm hp+ defect repair verification with scanner conditions

- Strategy for 2013 HVM:

- HVM tool requires commercial partner, but market is small

- Consortium model attempts underway July summit

Patterned:

- Industry Requirement:

- Patterned defect inspection at 22nm HP

- KLA6XX will achieve 32nm and some 22nm HP performance

- Strategy for 2013 HVM:

- Market is sizeable and tool cost significant

- Suppliers unwilling to bear \$250M NRE cost alone July summit

- SEMATECH contribution will be to broker funding model

## **EUV Mask Inspection Tools Summary**

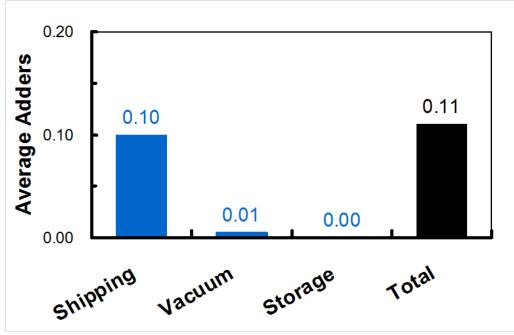

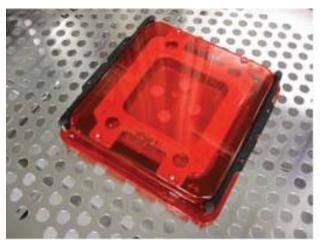

## **Particle-free Reticle Handling Progress**

He, et al. – Proc. SPIE <u>6921</u>, 69211Z (March 21, 2008)

E152 standard compliant prototype (sPod) shows reticle protection down to 0.1 added particles per lifecycle @53 nm.

sPod Carrier

#### with Inner Pod Exposed

## **EUV Pellicle Demonstration**

Hexagonal Ni mesh + Si membrane

- high risk/cost backup project

- full size pellicle demonstrated

- uniformity impact studies underway varying standoff height and mesh size

## **In-situ Inspection**

Need to verify reticle cleanliness AFTER loading into scanner and BEFORE printing wafers

- Repeater concern is serious due to lack of pellicles

- ArF scanners have in-situ reticle inspection capability

Not having in-situ capability would require printing of defect look-ahead wafers

- Manageable in development and perhaps in pilot line mode

- Unacceptable for HVM

Need focus from tool vendors to have capability avaialable in HVM tooling platforms

### **Reticle Technical and Infrastructure Gaps**

Current reticle defectivity gap is about 25-100X

- Need continuous improvement

- Relaxation of flatness spec might help bridge gap

- Inspection gaps

- Actinic blank inspection

- Patterned defect inspection spec vs. actual

- In-situ inspection

- AIMs inspection

SEMATECH is adopting a "bridge" tool solution for actinic blank and AIMS inspection so that some capability will be available for "pilot line" in 2011

Production actinic inspection, AIMS, and patterned inspection will require industry-wide funding (July workshop)

## **Summing Up**

Sivakumar **45**

2009 International Workshop on EUV Lithography

## **HVM Gaps - Overall**

|                               | Suppliers building solutions? | Estimated Cost for<br>HVM Solution | Time to HVM<br>Solution |

|-------------------------------|-------------------------------|------------------------------------|-------------------------|

| Full field production scanner | Yes                           | Funded                             | 2012                    |

| Source                        | Yes                           | Funded                             | 2011                    |

| Resist                        | Yes                           | Funded                             | 2011                    |

| Mask Blank                    |                               |                                    |                         |

| Multilayer Dep                | Yes                           | Funded                             | 2013                    |

| Actinic Blank Inspection      | No                            | >50M                               | 2013?                   |

| Actinic Defect Review         | No                            | >50M                               | 2013?                   |

| Mask Patterned Inspection     | No                            | >100M                              | 2013?                   |

Table from Bryan Rice, Sematech

SEMATECH's EUV mask infrastructure strategy is:

- Obtain support from various partners (public and private)

- Commit most of SEMATECH's Litho budget to mask infrastructure over next four years

Need industry consensus on required funding to bridge gaps

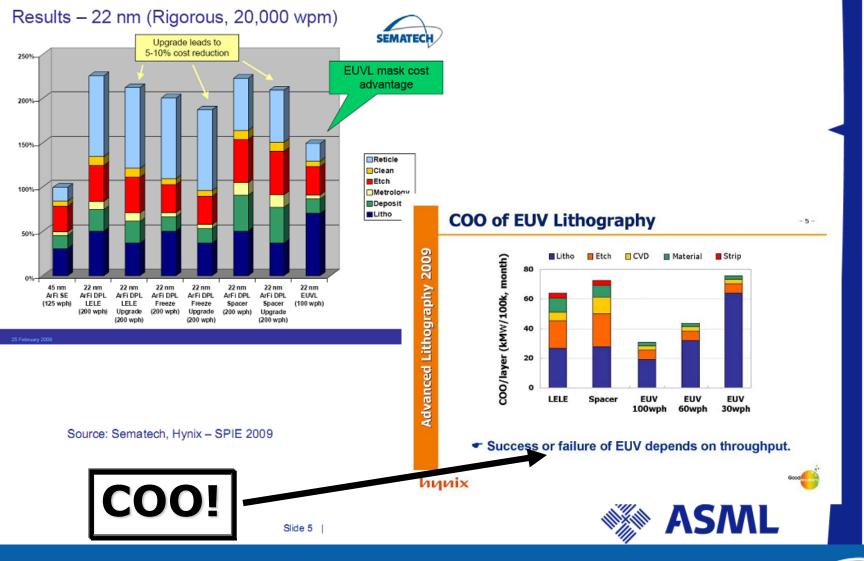

## **EUV Cost-Effectiveness**

2009 International Workshop on EUV Lithography

## No Exponential is forever, but we can delay "forever" – Gordon Moore

# Will EUV performance and COO enable us to continue to delay "forever?"

## Conclusions

Substantial progress made on resist and tooling

- Resists typically about 2X from goal for sensitivity/LWR

- Laser power about 10X from goal

- Overall tool runrate requires ~ 20X improvement to 100wph goal

Reticle defectivity is a major concern

- Blank defectivity needs substantial improvement

- Relaxation of flatness requirement might provide some mitigation

- Reticle inspection capability has major gaps. Need industry funding to enable tooling to be developed in time for HVM

Academic exercise is over!!

- EUV has moved from research to implementation mode

- Problems left to be solved are largely engineering in nature

- Need sustained focus and industry-wide commitment to solve

# Ultimately EUV insertion will be based on a COO decision vs. ArF