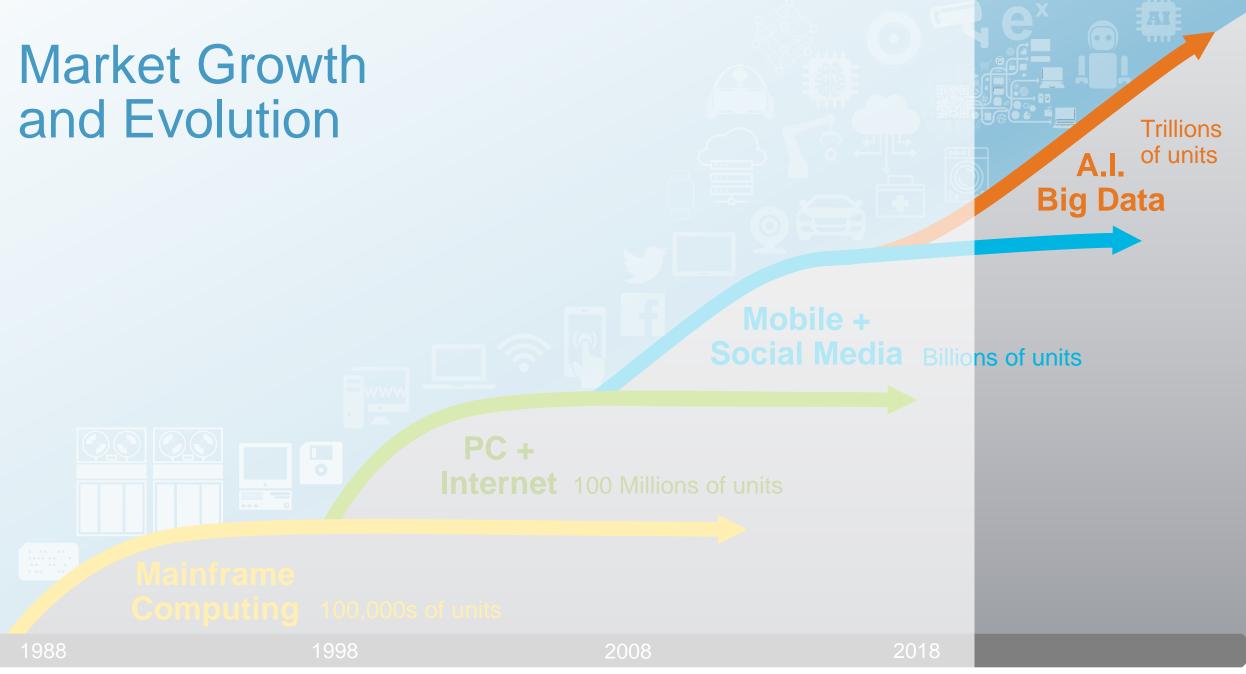

# Enabling the Semiconductor Roadmap from a Multi-Angled Approach

June 13<sup>th</sup>, 2019 Steven Welch Senior Director of Strategy, Advanced Product and Technology Development, Applied Materials

### Introduction

Steven Welch is currently Senior Director of Strategy for Applied Materials' Advanced Product and Technology Development group. In this role, he is responsible for identifying and synthesizing key inflections in the longer-term Semiconductor technology roadmap, as well as enabling disruptive technology development and business growth strategies to intercept these emerging opportunities. With over 20 years in the industry, Steven started his career in 1998 as a photolithography engineer at IBM's Storage Systems Division in San Jose, California. Since then, he has held marketing and strategy leadership positions in KLA-Tencor's wafer inspection, Applied Materials' etch, and ASML's holistic lithography businesses. Steven holds a B.S. in Chemistry from Harvey Mudd College and MA & MBA degrees from the University of Pennsylvania's Wharton School of Business.

**NDA** J

Semiconductor Scaling and Enablers

Logic Scaling Advancements

Memory Advancements to Scale A.I. Big Data

**NDA** J

### Semiconductor Scaling and Enablers

### Logic Scaling Advancements

### Memory Advancements to Scale A.I. Big Data

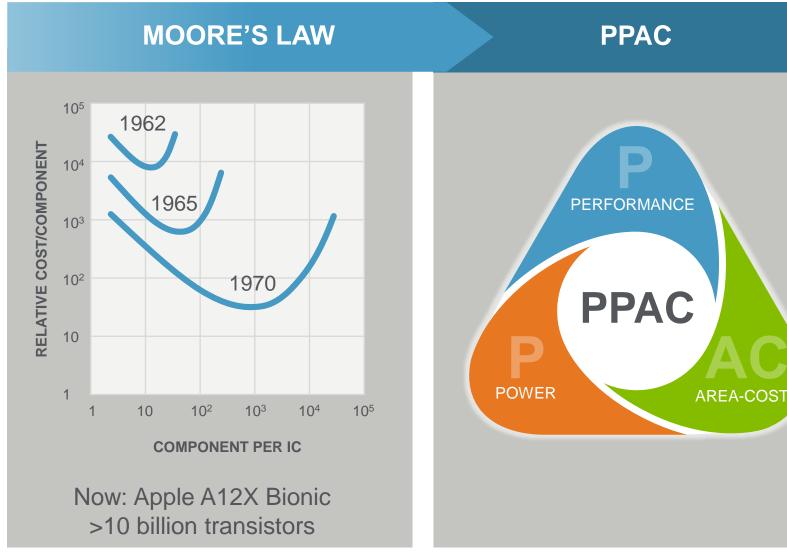

# Industry's Old Playbook...

#### **ENABLED BY**

"Classic" 2D feature shrinking

materials engineering to drive power and performance

https://wccftech.com/apple-a12x-10-billion-transistors-performance/

# In the Future...

#### ENABLED BY

New architectures

New structures / 3D

New materials

New ways to shrink

Advanced packaging

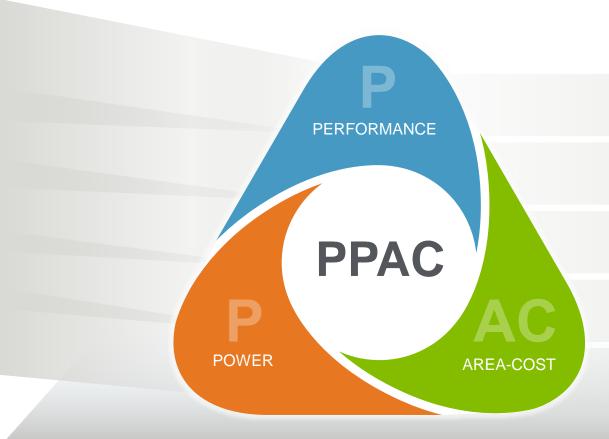

# ... New industry playbook needed to drive PPAC

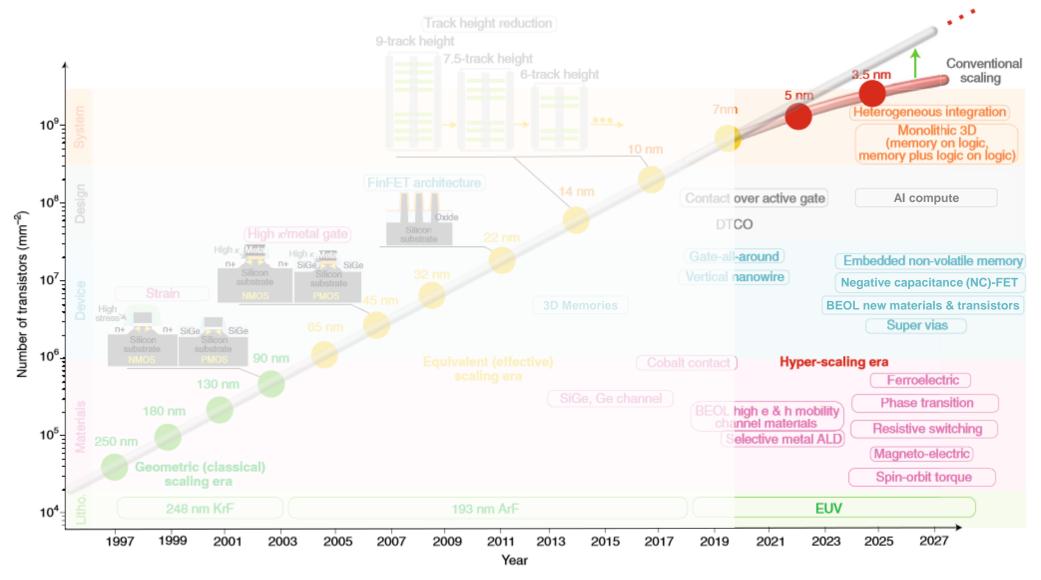

# Moore's Law beyond 5nm Node?

Adapted from Nature Electronics, V1, August' 2018, 442–450

APPLIED

MATERIALS

**NDA** J

### Semiconductor Scaling and Enablers

### Logic Scaling Advancements

### Memory Advancements to Scale A.I. Big Data

# **CMOS Scaling and Enablers**

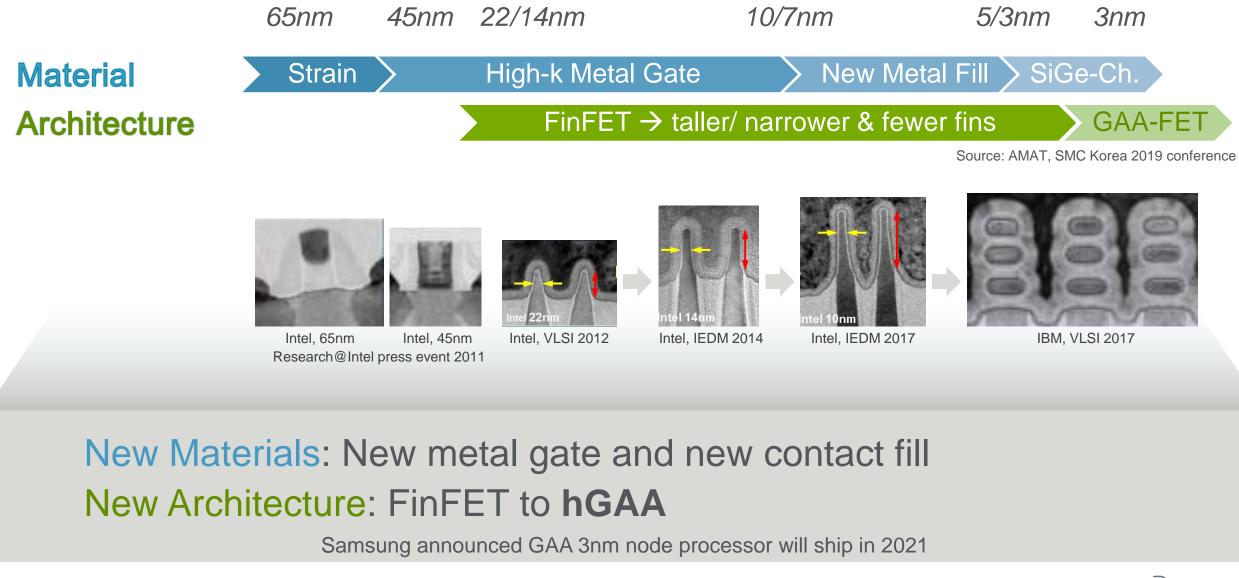

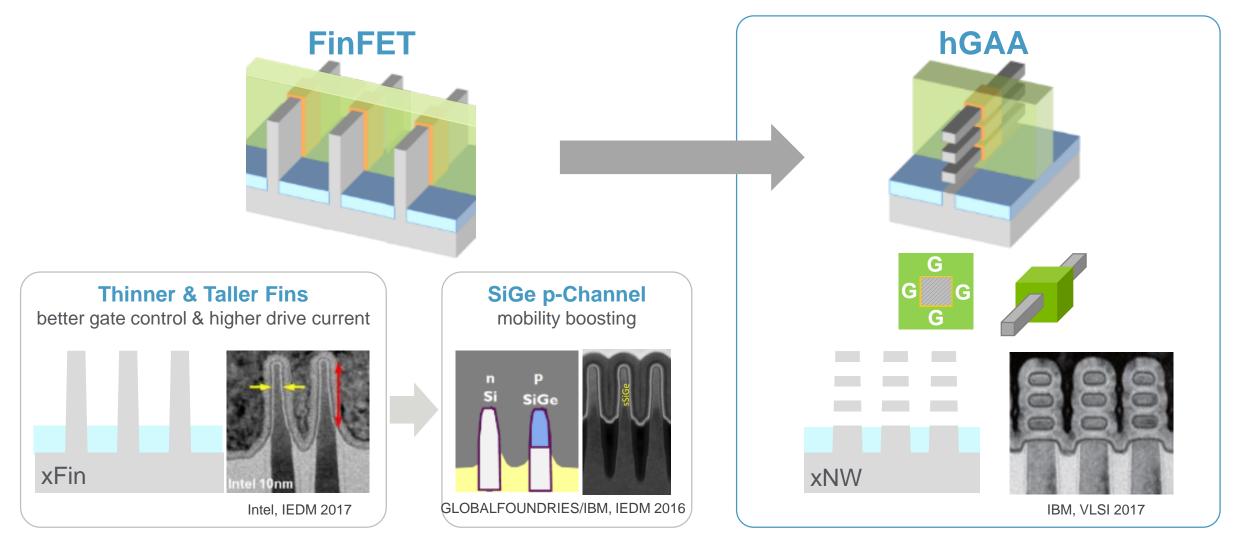

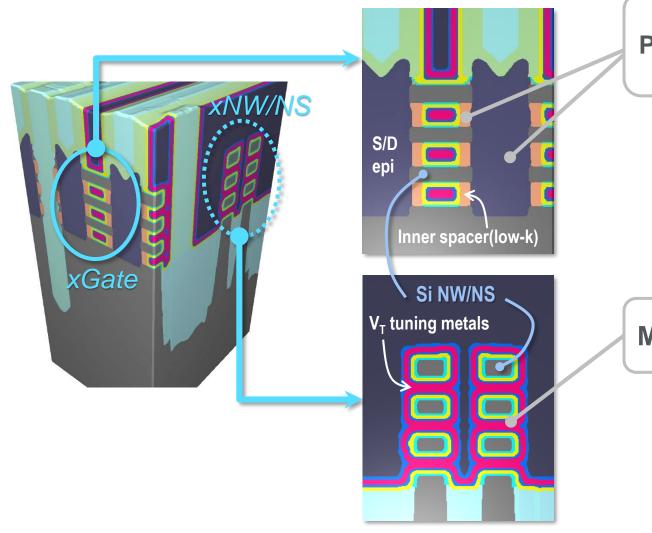

# Why *Horizontal*-GAA -> Evolutional Change

Vertically stackable channel (NW/NS) for increased current per area Similar structures & flows: hGAA vs. FinFET

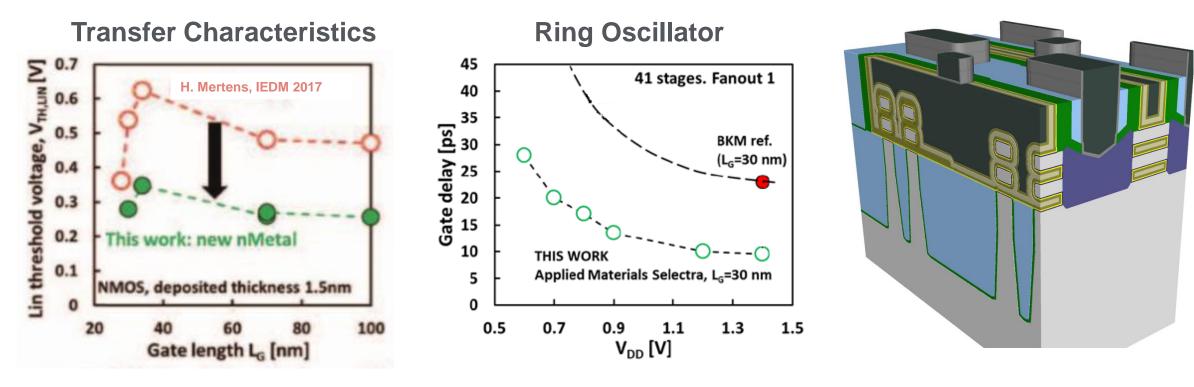

# **hGAA CMOS Initial Demonstrations**

Source: IMEC/ Applied Materials, IEDM 2018

### Functional CMOS demonstrated – getting ready for ≤3nm-node

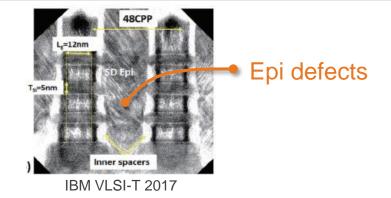

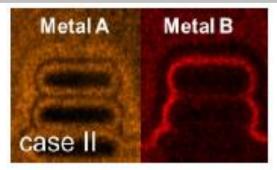

# hGAA CMOS – Key Challenges

Source: AMAT, SMC Korea 2019 conference

Parasitic capacitance reduction between sheets

#### Metal-gate Vt tuning in narrow gaps

IBM, IEDM 2017

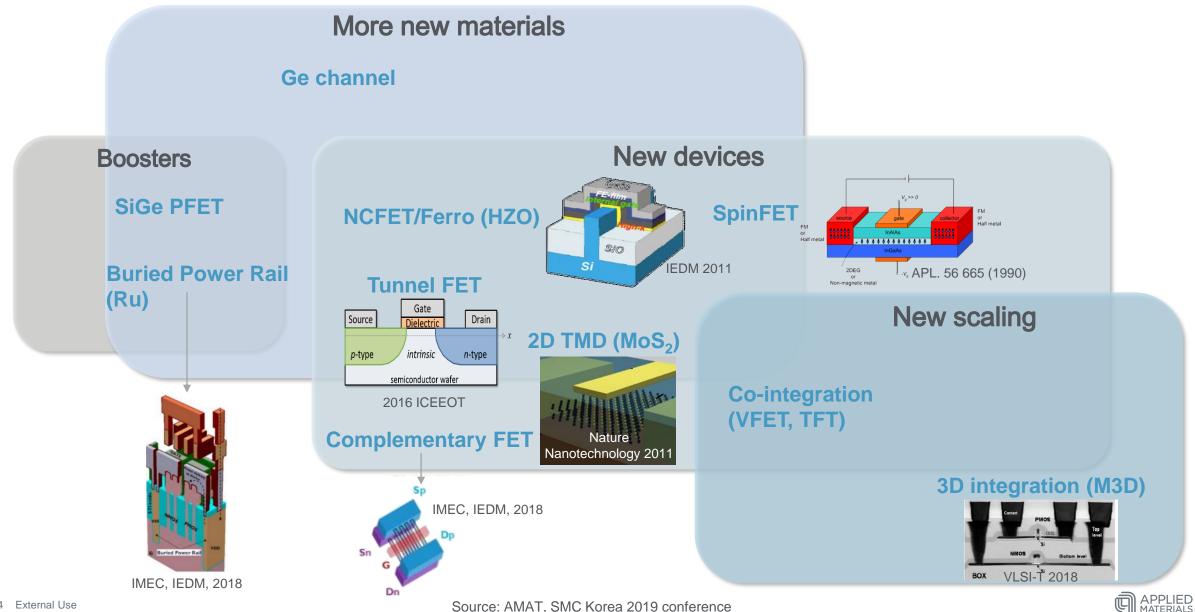

# **Beyond Conventional CMOS (≤2nm)**

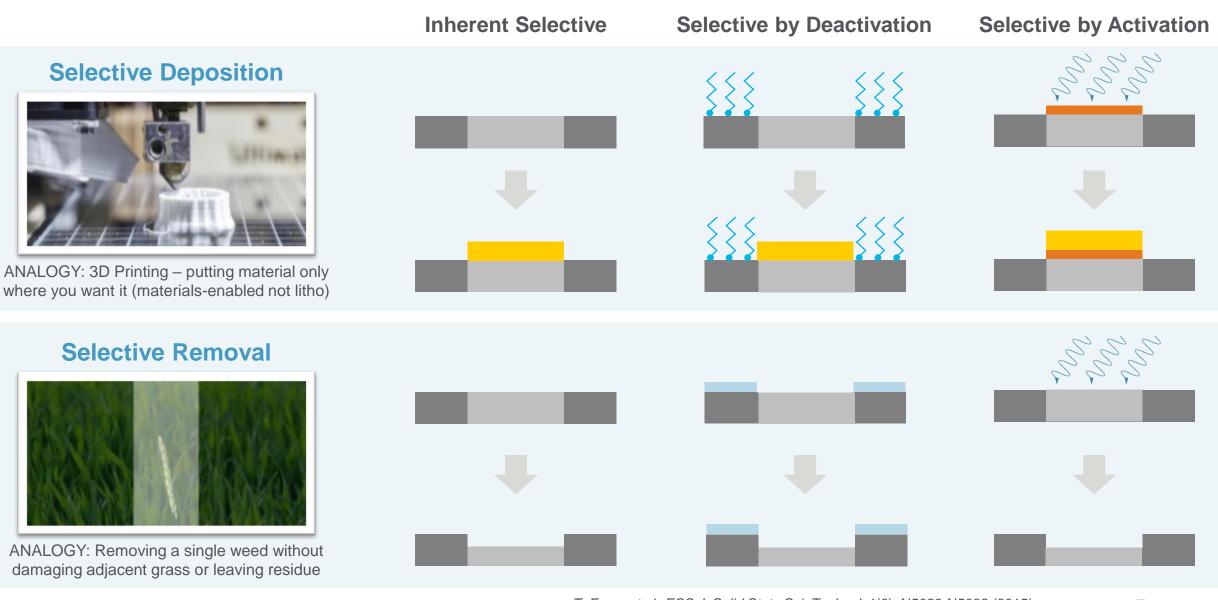

# **Selective Processes – Enabling New Ways to Build Chips**

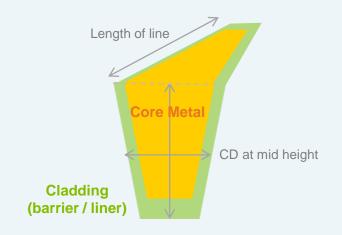

# **Scaling Opportunities in the Back-end-of-line Interconnect**

Source: AMAT, IEDM 2018 conference

BEOL Cu wire resistance (R) increasing at smaller geometries due to:

- Inherent bulk conductor resistivity characteristics

- Trade-off fill volume of highconducting vs. cladding materials

- Scattering at surfaces and grain boundaries

...resulting in slower performance and higher power consumption

Materials-Engineering Solutions:

- ▶ New materials (lowest R at CD)

- Full-volume metal fills

- Interface management

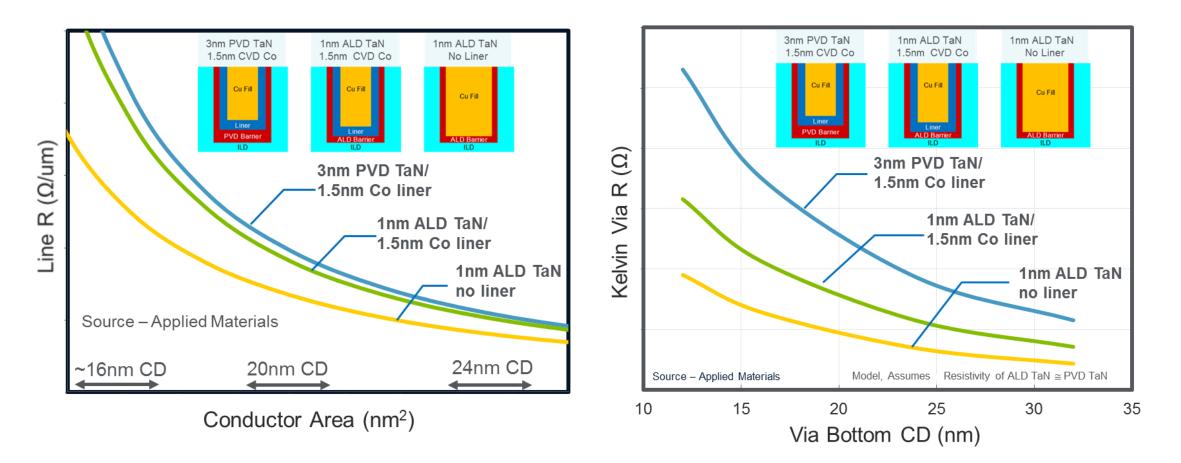

# **Copper Extension Scenarios**

Co-optimization of ALD barriers with thinner liners and new fill technology is key to maximize conductor volume (low line R) and minimize interface resistance (low via R)

Source: AMAT, IEDM 2018 conference

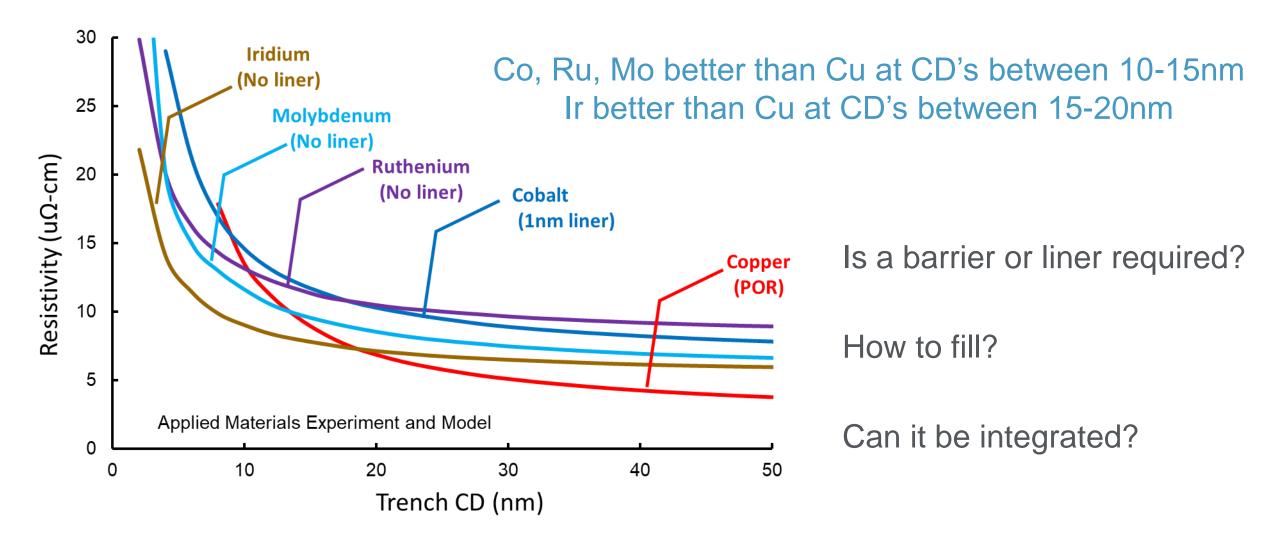

# **New Metals for Resistance Scaling**

**NDA** J

### Semiconductor Scaling and Enablers

### Logic Scaling Advancements

### Memory Advancements to Scale A.I. Big Data

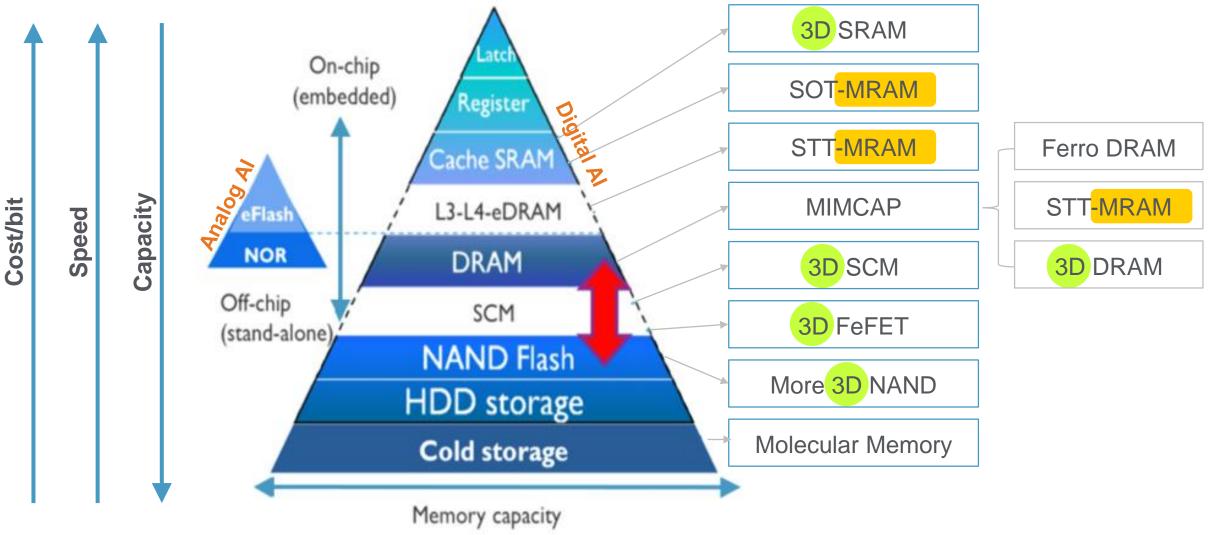

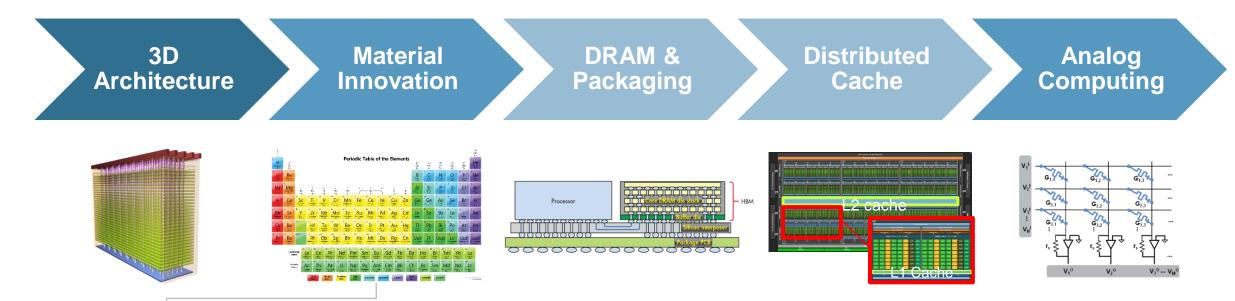

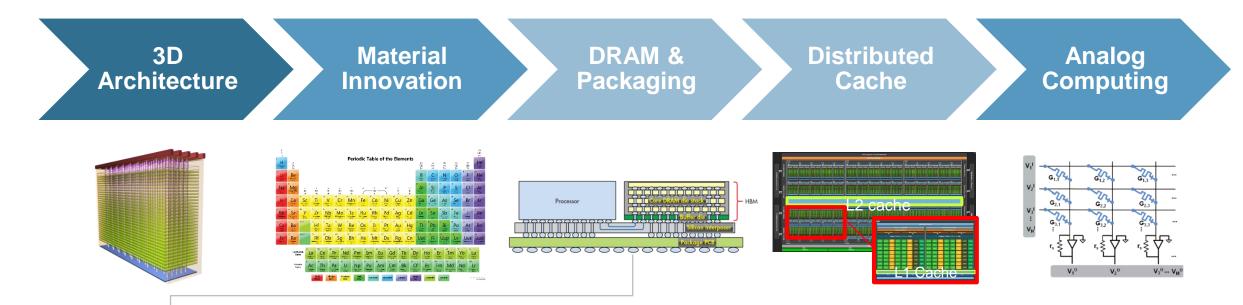

# **Emerging Memories for Pervasive Data and Compute**

**APPLIED** MATERIALS

Source: <u>http://www.imec.be</u> from techspot.com (February 21, 2019)

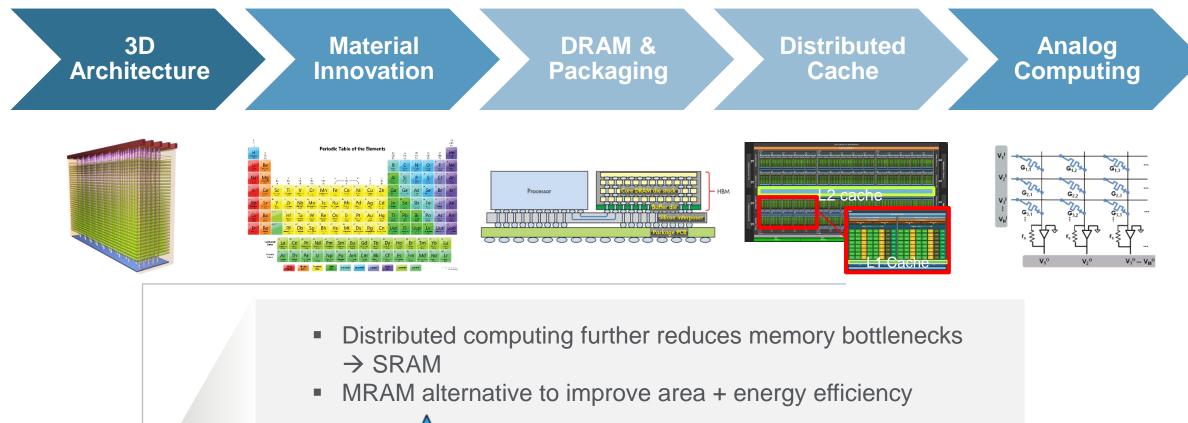

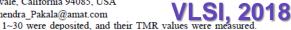

# **Architectural Advancements Leveraging Memory & Design**

# Significant investments in memory to enable better bit scaling and performance

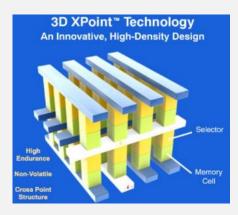

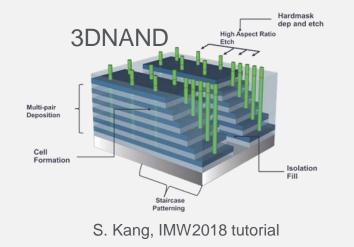

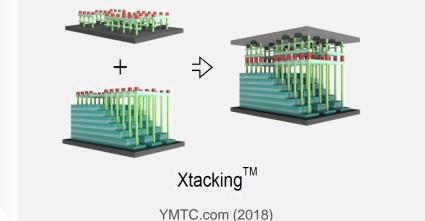

# **3D Architectures**

#### 3D architectures extend memory densities

Source: Intel 2015

# **3D Architectures**

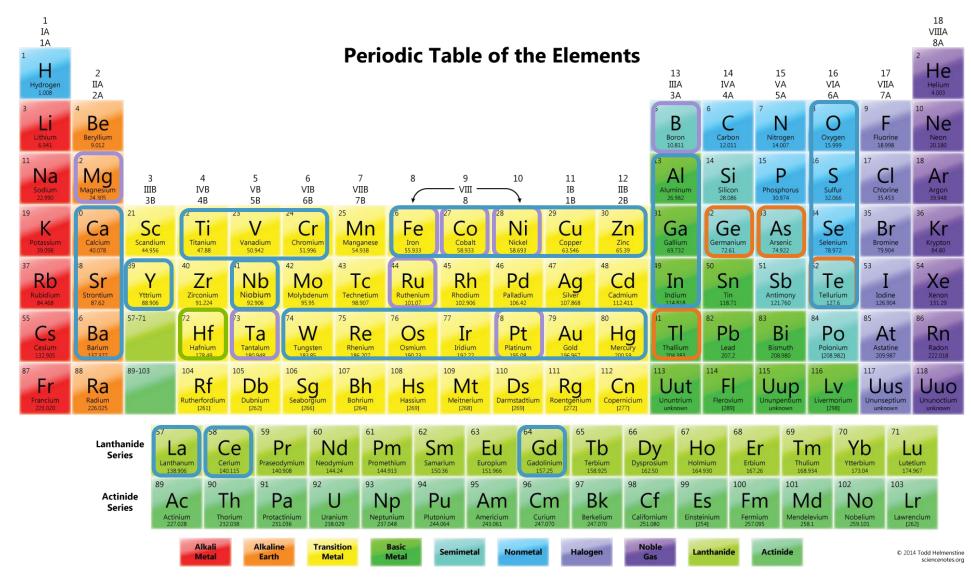

#### Materials and Interfaces

- Complex stacks with multiple exotic materials are required to enable new memories

- Deposition, etch and CMP are critical process development areas

Deposition

Etch

**Planarization**

# **Example of Elements to Enable New Memories**

#### **PCM Selector**

- M-K. Lee, IEDM 2012

- G.H. Kim, APL 2012

- L. Zhang, IEDM 2014

#### **STT-MRAM**

K. Ando, JAP 2014

#### FE-FET

- X. Tian, APL 2018

- A. Pal, APL 2017

### CBRAM

Adesto Technologies, IEEE 2013 talk

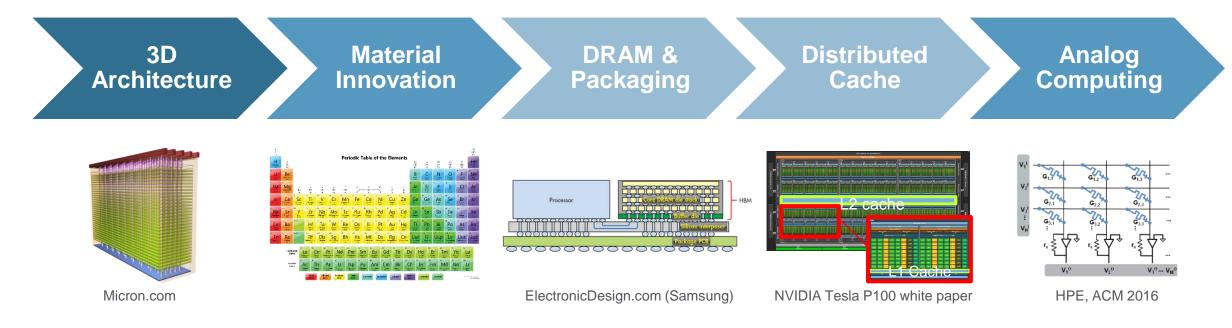

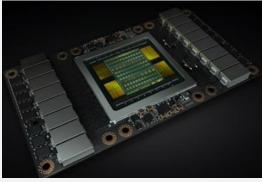

# **DRAM and Packaging**

Packaging enables higher performance to support more complex workloads

Nvdia V100 source: techreport.com 2017

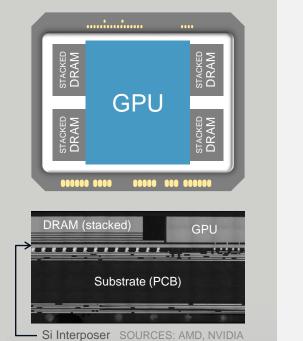

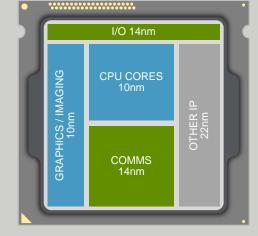

# **Beyond Chip Scaling: Advanced Packaging**

#### DRAM ON PCB to STACKED DRAM IN PACKAGE

#### HETEROGENEOUS INTEGRATION

**3x** Logic ←→ DRAM bandwidth performance

**50%** Power savings per bit

SOURCES: Intel, GLOBALFOUNDRIES System on Chip to System on Package

Integration of chiplets provides **time, cost** and **yield** benefits

### Connecting chips together in new ways using advanced packaging

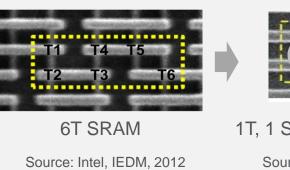

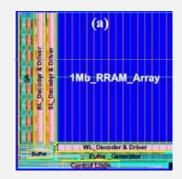

# **Distributed Cache**

1T, 1 STT-MRAM

Source: AMAT

### **Multiple MRAM Milestone Announcements**

|                                                                                                                                                                                                                                                                                   |                                                                                                                                                                         | S                                                                                                                                        |                                                                                                                                                   | intel                                                                                                                              | SAMSUNG                                                                                                                       |                                                                                                                                   | SAMSUNG                                                 |

|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------|-------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------|---------------------------------------------------------|

| <ul> <li>8/2017</li> <li>Everspin<br/>announced<br/>sampling of<br/>the world's<br/>first 1Gb<br/>MRAM<br/>product</li> <li>9/2017</li> <li>Global<br/>Foundries<br/>announced<br/>availability of<br/>embedded<br/>MRAM on<br/>leading<br/>22FDX FD-<br/>SOI platform</li> </ul> | 7/2018<br>TSMC<br>"Over 50<br>customers and<br>140 tapeout in<br>N22ULP,<br>spanning<br>many<br>application<br>areas<br>connectivity,<br>digital TV/STB,<br>application | 11/2018<br>Spin Memory<br>& Applied<br>Materials<br>commercial<br>agreement to<br>create a<br>comprehensive<br>embedded<br>MRAM solution | 12/2018<br>Gyrfalcon<br>Technology<br>announced<br>the<br>commercial<br>availability of<br>its AI ASIC<br>that include<br>TSMC's<br>22nm<br>eMRAM | <b>12/201</b><br><b>Intel</b><br>described the<br>first FinFET-<br>based<br>MRAM<br>technology<br>(22nm) is<br>production<br>ready | 8 IEDM conf<br>Samsung<br>showed<br>MRAM<br>design<br>technology<br>co-<br>optimization<br>for hardware<br>neural<br>networks | erence<br>Global<br>Foundries<br>showed<br>22nm<br>embedded<br>40 Mb<br>MRAM for<br>low-power<br>automotive<br>MCU<br>application | 3/2019<br>Samsung<br>shipped the<br>first 28nm<br>eMRAM |

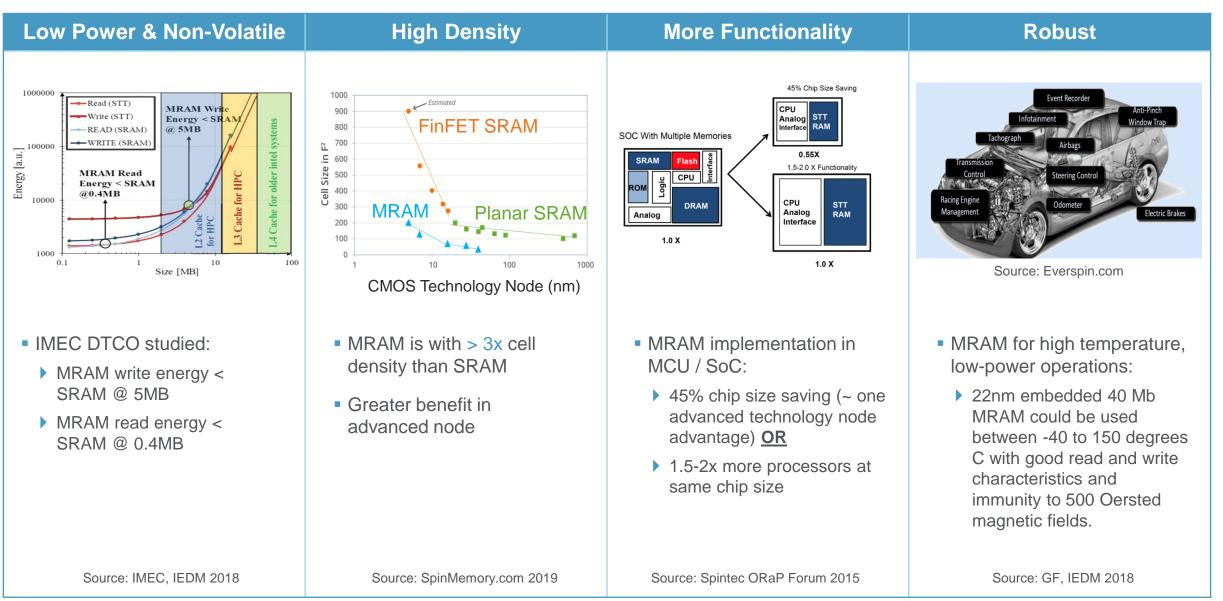

# **MRAM Benefits**

# **MRAM Capability Demonstrated by Optimization of Complex Stack**

| Top electrode               |

|-----------------------------|

| MgO capping                 |

| Free layer<br>(CoFeB based) |

| MgO barrier                 |

| Reference layer             |

| Ru                          |

| Pinned layer                |

| Seed                        |

| Bottom electrode            |

|                             |

Sources: Applied Materials

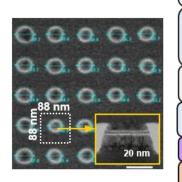

Systematic Optimization of 1 Gbit Perpendicular Magnetic Tunnel Junction Arrays for

IEDM, 2015

28 nm Embedded STT- MRAM and Beyond

C. Park<sup>1,a</sup>, J.J. Kan<sup>1</sup>, C. Ching<sup>2</sup> Hassan<sup>2</sup>

Systematic Validation of 2x nm Diameter Perpendicular MTJ Arrays and MgO

Barrier for Sub-10 nm Embedded STT-MRAM with Practically Unlimited Endurance

J.J. Kan<sup>1,a</sup>, C. Park<sup>1</sup>, C. Ching<sup>2</sup>, J. Ahn<sup>2</sup>, L. Xue<sup>2</sup>, R. Wang<sup>2</sup>, A. Kontos<sup>2</sup>, S. Liang<sup>2</sup>, M. Bangar<sup>2</sup>, H.Chen<sup>2</sup>, S.

Hassan<sup>2</sup>, S. Kim<sup>1</sup>, M. Pakala<sup>2,b</sup>, and S. H. Kang<sup>1</sup>

**IEDM, 2016**

<sup>1</sup>Qualcomm Technologies, Inc., San Diego, California 92121, USA. E-mail: <sup>a</sup>jkan@qti.qualcomm.com

endra\_pakala@amat.com

#### Low RA Magnetic Tunnel Junction Arrays in Conjunction with Low Switching Current and High Breakdown Voltage for STT-MRAM at 10 nm and Beyond PENDICULAR MTJ DEVICES

C. Park<sup>1,a</sup>, H. Lee<sup>1</sup>, C. Chiu <sup>1</sup> Corporate Research and Development, Qualcomm <sup>2</sup>Silicon Systems Group, App

<sup>1</sup>Oualco

<sup>2</sup>Silicon Systems

"Tel: 1-858-658-1890, "ch

#### **VLSI. 2018**

Abstracts

The scaling of STT-MRAM for deeply scaled nod 10 nm CMOS) requires low resistance-area-pr magnetic tunnel junctions (MTJs) to contair voltage (V<sub>c</sub>) and to assure high endurance. In various reports, we demonstrate systematic eng low-RA MTJs without trading off key device at remarkably, with higher barrier reliability. The MT an ultra-thin synthetic antiferromagnetic layer (tf Co/Pt pseudo-alloy pinned layer. By reducing R4 5  $\Omega \mu m^2$ , significantly reduced V<sub>c</sub> and reliable sw ns have been achieved. Furthermore, the breakdd (V<sub>BD</sub>) has been improved. The results sugge tunability of MTJ is extended to sub-10 nm CMC performance and high-reliability MRAM. Process Optimization of Perpendicular Magnetic Tunnel Junction Arrays for Last-Level Cache beyond 7 nm Node

Lin Xue<sup>a</sup>, Chi Ching, Alex Kontos, Jaesoo Ahn, Xiaodong Wang, Renu Whig, Hsin-wei Tseng, James Howarth, Sajjad Hassan, Hao Chen, Mangesh Bangar, Shurong Liang, Rongjun Wang, Mahendra Pakala<sup>b</sup>

Applied Materials, Inc., Sunnyvale, California 94085, USA <sup>a</sup> Lin Xue@amat.com, <sup>b</sup> Mahendra Pakala@amat.com

Abstract

This paper demonstrates systematic process optimization of perpendicular magnetic tunnel junction (pMTJ) by hardware, unit-process, and material stack design. TMR of 200% at RA 5 Ohm  $\mu$ m<sup>2</sup>, H<sub>SAF</sub> ~ 8 kOe, and 10-time tunability of Hc were achieved at the film level. After patterning, 10<sup>-6</sup> write error rate was reached at 0.4 pJ, V<sub>BD</sub> was as high as 1600 mV at 20 ns pulse width, and excellent device stability against 400°C BEOL baking was demonstrated. The device performance along with the process capability to make MTJ array at 88 nm pitch provides opportunities for LLC applications.

Introduction STT-MRAM has become one of the leading new memory

technologies as it demonstrated excellent scalability and low

200% was achieved at RA of 5 Ohm·µm<sup>2</sup>, relevant to LLC applications. TMR ~ 100% was measured at RA ~ 1 Ohm·µm<sup>2</sup>. The results showed excellent RA scalability of MTJ films. The magnetic properties of the MTJ stack were improved by testing different materials for capping and SAF coupling. Fig. 4 shows films of four different materials of capping with Hc from 8 to 80 Oe. No obvious change of RA or TMR was measured. High SAF coupling (H<sub>SAF</sub>) of the MTJ film allows low write error rate. By optimizing SAF coupling material as well as magnetic material thickness within the reference layer, H<sub>SAF</sub> increased from 4 to 8 kOe (Fig. 5). **Device and Array Performance**

Although lower polarization at lower RA limits TMR, TMR of

### Roadmap for additional density and performance scaling in development

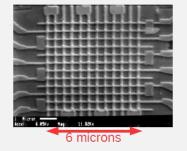

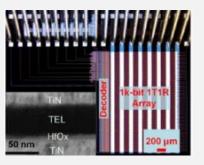

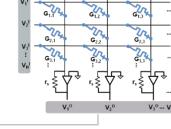

# **Digital to Analog Computing**

Analog vector-matrix multiplier: reduced complexity and power; will require further advances in process variability

12x12 array, Bell Labs 1986 cited by LeCuin, ISSCC 2019

**CAS, IEDM 2017**

Tsinghua, IEDM 2017

**APPLIED** MATERIALS

# **Emerging Memory for Machine Learning Accelerators**

**1. Digital Accelerator** SRAM → MRAM available in Foundry

"The 2802M ASIC has 40MB of eMRAM memory, which can support large AI models or multiple AI models within a single chip." – gyrfalcontech.ai 2019

• MRAM can enable area benefit at lower power versus traditional distributed SRAM techniques

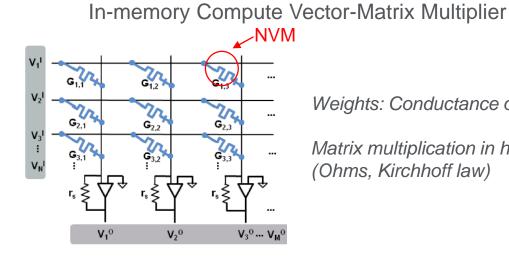

#### 2. Analog Accelerator

#### eFlash → RERAM, FEFET, PCRAM in Development

Weights: Conductance of NVM

Matrix multiplication in hardware (Ohms, Kirchhoff law)

"1,000 to 10,000 better speed-energy efficiency product than digital ASICs" - HPE, ACM 2016

New analog memories, once performance at scale is robust, can enable additional performance boosts @ density and new ways of compute

# **PPAC Optimization Beyond the Chip**